بهینه سازی ساختار ترانزیستور قدرت برای کاربرد در فرکانس بالا و تجهیزات پزشکی

بهینه سازی ساختار ترانزیستور قدرت برای کاربرد در فرکانس بالا و تجهیزات پزشکی

بهینه سازی ساختار ترانزیستور قدرت برای کاربرد در فرکانس بالا و تجهیزات پزشکی

فرمت: WORD تعداد صفحات: 12

چکیده:

مقدمه:

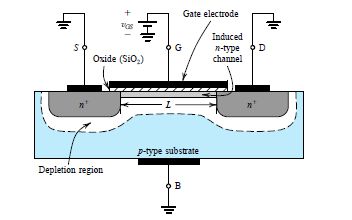

ترانزیستورهای قدرت یکی از پرکاربردترین المان ها در مدارات تقویت کننده تجهیزات پزشکی می باشند که از مهمترین آنها می توان به VDMOS اشاره کردهدف از این پژوهش ساخت یک ترانزیستور قدرت Vertical Double-Diffused Metal-Oxide Semiconductor (VDMOS) با ساختار بهینه شده، برای بهبود عملکرد تجهیزات پزشکی بوده است.

روش تحقیق

روش تحقیق مطالعاتی- کاربردی بود. نقطه شروع بهینه سازی شامل مراحل کاشت عنصر برون به داخل سیلیکون به کمک کاشت های UIS و فارادی انجام گرفت. کاشت پوسته فارادی به منظور جابه جا کردن خازن پارازیتی گیت – میدان روی قسمت ورودی قطعه انجام شد، که به طور چشم گیری پاسخ فرکانسی قطعه را بهبود بخشید. کاشت UIS (Unclamped Inductive Switching)، به منظور کاهش Bipolar Junction Transistor (BJT) پارازیتی ترانزیستور قدرت VDMOS استفاده شد. ابزار کار ما در این تحقیق نرم افزار سیلواکو بود.

یافته ها:

با افزایش ولتاژ شکست از 82 ولت به 86 ولت، عملکرد ترانزیستور VDMOS را برای کاربرد های مختلف از جمله کاربرد در فرکانس بالا و تجهیزات پزشکی بهبود بخشیدیم، در این پژوهش ولتاژاستانه از 3.2 ولت به 2.75 ولت تغییر داده شد، که با این کار خازن ورودی VDMOS سریع تر شارژ و در نتیجه سریع تر دشارژ شد که با این کار زمان خاموش و روشن شدن ترانزیستور VDMOS کاهش یافت، که در نتیجه فرکانس نیز افزایش یافت. همچنین میزان بهره جریان درین را از 4 میکرو آمپر به 5 میکرو آمپر رسید، که خود این افزایش جریان به بالا بردن سرعت سوییچینگ کمک کرد.

نتیجه گیری:

در ساختار VDMOS بهینه شده، با کم شدن مقاومت ورودی ترانزیستور، تلفات توان در ورودی ترانزیستورونویز کاهش یافت و با افزایش ولتاژ شکست، عمر ترانزیستور VDMOS افزایش یافت، در نتیجه باعث افزایش جریان درین و کاهش مقاومت روشنی شد، این امر باعث بهبود عملکرد فرکانس بالا و دستگاه های پزشکی که از ترانزیستور استفاده می نمایند از جمله دستگاه RF و دستگاه الکتروکاردیوگرافی شد و سرعت عملکرد آنها را بالا برد.

واژه های کلیدی: ترانزیستور VDMOS، کاشت UIS، دستگاه الکتروکاردیوگراف، نویز، فرکانس بالا

1.مقدمه:

1.1. background:

ترانزیستور VDMOS برای کاربرد قدرت وفرکانس بالا مدار تقویت کننده تجهیزات پزشکی، باید طول کانال کم و سطح آلایش پایین در ناحیه درین داشته باشد. داشتن سطح آلایش پایین در درین تضمین می کند که لایه فضای بار در پیوند درین – کانال، داخل ناحیه درین به جای ناحیه کانال گسترش یافته، و می تواند ولتاژ زیادی را مسدود کند.

تحقیقات انجام شده در این زمینه به این نتایج دست یافتند که، عملکرد در حالت خاموش، منجر به افزایش پتانسیل الکتروستاتیکی، مستقل از Vds خارجی می شود و این پتانسیل نگه دارنده به شکست زود هنگام پیوند اکسید گیت روی سطح کمک می نماید. با تخمین ایزولاسیون حرارتی به کار گرفته شده مقادیر ذاتی gm و Ron در این شرایط بهترین مقدار با محدود ولتاژ مشابه برای عملکرد فرکانس بالا بود.

عیبی که این روش داشت، این بود که BVDD این قطعات به ولتاژ شکست پیوند سطح صاف محدود شده بودند. برای مقادیر متوسط، پراکندگی ناحیه تخلیه به طور قوی تحت تاثیر گرادیان بزرگ آلاینده در ناحیه JFET قرار گرفت، در نتیجه وابستگی به زیاد شد. تحلیل و شبیه سازی عملکرد کاهش استرس روی ترانزیستورهای VDMOS قدرت انجام شد به این نتیجه رسیدند که استفاده از ترانزیستور های VDMOS تحت شرایط استرس به بهبود مشخصه های فیزیکی و الکتریکی از جمله و ولتاژ شکست منجرب شده و بار سطحی تحت شرایط استرس منفی بود [1].

عیبی که این روش دارد این است که هر چه زمان استرس را زیاد کنیم، تا حدی عملکرد VDMOS را بهبود می بخشد و اگر مدت زمان استرس را زیاد کنیم دیگر تاثیری روی بهبود عملکرد قطعه نخواهد داشت [1].

در تحقیقاتی که روی یک ترانزیستور VDMOS مسطح با اثر میدان ، با جزایر ناهمگون و شناور انجام گرفت به این نتیجه رسیدند که جزایر شناور ناهمگون در ترانزیستور های VDMOSFETدر ولتاژ شکست برابر، موجب کاهش 38% در Ron.sp نسبت به ساختار VDMOS معمولی شده است. 10% کاهش Ron.sp در ولتاژ شکست برابر نسبت به VDMOS با جزایر شناور همگون داشته است و همچنین با افزایش تعداد جزایر شناور ولتاژ شکست افزایش یافت[2].

ایراد این روش نیاز به ماسک اضافی برای رسیدن به جزیره های P ناهمگون است و هزینه ساخت این روش بیشتر و ساختار پیچیده تری دارد و VDMOS ارائه شده در این مطالعه در ولتاژهای پایین عملکرد بهتری دارد[2].

در تحقیقاتی که روی ارتقاء رویداد گسیختگی در گیت (single event gate-rupture SEGR) برای یک VDMOS انجام گرفت به این نتیجه رسیدند که ولتاژ ترشولد SEGR VDMOS نسبت به VDMOS معمولی 120% بهبود یافته و Ron در SEGR VDMOS به اندازه 15.5% نسبت به VDMOS معمولی بهبود پیدا کرده است، و این ساختار برای کاربردها با ولتاژ بالا مناسب می باشد [2].

عیبی که این روش دارد وجود ساختار LOCOS که روی ناحیه neck قرار دارد، برای VDMOS وابسته به ناحیه neck بوده است و در واقع در این ساختار یک trade-off بین Ron و ولتاژ شکست وجود دارد، یعنی با افزایش ولتاژ شکست Ron زیاد نیز زیاد می شود و با کاهش ولتاژ شکست مقاومت Ron نیز کم می شود [3].

در تحقیقاتی که روی ساختار جدید VDMOS با ضخامت ناپیوسته اکسید مدفون بدنه برای کاهش بار گیت به درین انجام شد به این نتیجه رسیدند که با این روش تزریق حاملان داغ به vdmos در مقایسه با ساختار مرسوم به طور قابل ملاحظه ای کاهش یافته و ترانزیستور VDMOS پیشنهاد شده بهترین Qgd×sRon را دارد [4].

1.2. Statement of the problem:

ترانزیستور VDMOS به دلیل داشتن ولتاژ شکست بالا و Ron پایین قطعه مهمی برای کاربردهای تجهیزات پزشکی و فرکانس بالا می باشد. برای استفاده از این ترانزیستور درکاربرد های قدرت و فرکانس های بالا و مدار تقویت کننده تجهیزات پزشکی ضروری است که را تا حد امکان کاهش دهیم، اما همیشه یک trade-off بین Ron و ولتاژ شکست وجود دارد، با پایین آمدن Ron ولتاژ شکست نیز کاهش می یابد در نتیجه کارایی قطعه را در ولتاژهای بالا (مبدل های قدرت و تجهیزات پزشکی) کاهش می دهد،این مشکل یکی از محدودیت های VDMOS می باشد[5].

کاهش ولتاژ شکست در سیستم های قدرت به خصوص مبدل های dc/dc و مدار تقویت کننده تجهیزات پزشکی که زیاد درآنها از VDMOS استفاده می شود منجربه صدمه دیدن مدار داخلی این مبدل ها شده و کندی المان، افزایش تلفات و کاهش عمر مبدل می شود[2].

همچنین در کاربردهای فرکانس بالا، اگر Ron زیاد شود موجب کاهش سرعت عملکرد تقویت کننده ها در کانال های گیرنده و فرستنده شده و تلفات زیادی را به بار خواهد آورد. از طرفی اگر Ron را کم کنیم به دنبال آن ولتاژ شکست نیز افت خواهد کرد که اگر این افت ولتاژ شکست خیلی زیاد باشد دیگر ترانزیستور VDMOS برای کاربرد های قدرت، مناسب نخواهد بود.

از آنجایی که جهت عبور جریان در این قطعه از درین به سورس به صورت عمودی است و هنگام عبور جریان از درین به سورس مقاومت های زیادی سر راه جریان وجود دارند، باعث افزایش Ron می شوند و مقدار این مقاومت به ساختار فیزیکی قطعه وابسته است[2]. کاهش ترانزیستور VDMOS به دلیل تشکیل افزاره پارازیتی JFET سخت است.

ورود یا ثبـــت نــــام + فعال کردن اکانت VIP

مزایای اشتراک ویژه : دسترسی به آرشیو هزاران مقالات تخصصی، درخواست مقالات فارسی و انگلیسی، مشاوره رایگان، تخفیف ویژه محصولات سایت و ...

حتما بخوانید:

⇐ واژه نامه سترونی تجهیزات پزشکی یکبار مصرف با گاز اکسید اتیلن

دیدگاه خود را ثبت کنید

تمایل دارید در گفتگوها شرکت کنید؟در گفتگو ها شرکت کنید.